#### Register 0 and 1: Input port 0 and 1 registers (input-only port).

It reflects the incoming logic levels of the pins, regardless of whether the pin is defined as an input or an output. Writes to this register have no effect. The default value 'X' is determined by the externally applied logic level.

| Bit                   | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|-----------------------|------|------|------|------|------|------|------|------|

| Input port 0 register | 10.7 | 10.6 | 10.5 | 10.4 | 10.3 | 10.2 | 10.1 | 10.0 |

| Input port 1 register | 11.7 | I1.6 | 11.5 | 11.4 | I1.3 | I1.2 | 11.1 | 11.0 |

| Default               | Χ    | Χ    | Χ    | Χ    | Χ    | Χ    | Χ    | Χ    |

#### Register 2 and 3: Output port 0 and 1 registers (output-only port).

It reflects the outgoing logic levels of the pins defined as outputs. Bit values in this register have no effect on pins defined as inputs.

| Bit                    | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|------------------------|------|------|------|------|------|------|------|------|

| Output port 0 register | O0.7 | O0.6 | O0.5 | O0.4 | O0.3 | O0.2 | O0.1 | 0.00 |

| Output port 1 register | 01.7 | O1.6 | O1.5 | 01.4 | O1.3 | 01.2 | 01.1 | O1.0 |

| Default                | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

#### Register 4 and 5: Polarity inversion port 0 and 1 registers.

This register allows the user to invert the polarity of the Input port register data. If a bit in this register is written with '1', the Input port data polarity is inverted. If a bit in this register is written with '0', the Input port data polarity is retained.

| Bit                       | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------------------------|------|------|------|------|------|------|------|------|

| Polarity inversion port 0 | N0.7 | N0.6 | N0.5 | N0.4 | N0.3 | N0.2 | N0.1 | N0.0 |

| Polarity inversion port 1 | N1.7 | N1.6 | N1.5 | N1.4 | N1.3 | N1.2 | N1.1 | N1.0 |

| Default                   | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

#### Register 6 and 7: Configuration port 0 and 1 registers.

This register configures the directions of the I/O pins. If a bit in this register is written with '1', the corresponding pin is enabled as an input. If a bit in this register is written with '0', the corresponding pin is enabled as an output. At reset, the device's ports are inputs.

| Bit                  | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|----------------------|------|------|------|------|------|------|------|------|

| Configuration port 0 | C0.7 | C0.6 | C0.5 | C0.4 | C0.3 | C0.2 | C0.1 | C0.0 |

| Configuration port 1 | C1.7 | C1.6 | C1.5 | C1.4 | C1.3 | C1.2 | C1.1 | C1.0 |

| Default              | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

Note: Please contact your local vendors if any damaged or missing items. DO NOT apply power to the module if there is any damaged component.

94193285000E ©Copyright 2015 Axiomtek Co., Ltd. Version A1 April 2015 Printed in Taiwan

# AX93285 ZIO Module Quick Installation Guide

### Checklist

√ I/O board x1

√ Screw pack x1

✓ Quick installation guide x1

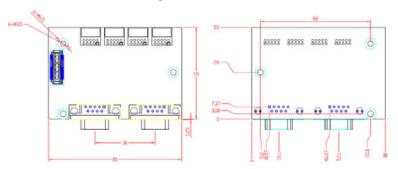

## **Dimension and Fixing Holes**

### **Module Layout**

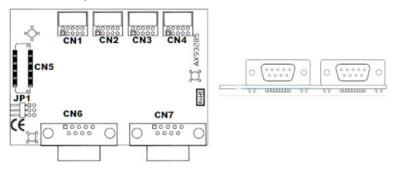

### **Connectors**

| Connector | Description             |  |

|-----------|-------------------------|--|

| CN1~CN4   | Digital I/O Connectors  |  |

| CN5       | ZIO Expansion Connector |  |

| CN6       | COM1 Connector          |  |

| CN7       | COM2 Connector          |  |

94193285000E

©Copyright 2015 Axiomtek Co., Ltd.

Version A1 April 2015

Printed in Taiwan

1

#### Digital I/O Connectors (CN1~CN4)

CN1~CN4 are JST B10B-PHD-S-S, 2x5-pin P=2.0mm Dip connectors for digital I/O interface that meet requirements for a system customary automation control. These digital I/O signals are from two 16-bit PCA9535 and controlled through SMBus:

- First group (CN1 and CN2), SMBus address: 0x40.

- Second group (CN3 and CN4), SMBus address: 0x44.

#### CN1/CN2/CN3/CN4:

2

| Pin | Signal       | Pin | Signal       |

|-----|--------------|-----|--------------|

| 1   | GND          | 2   | +5V level    |

| 3   | DI4/12/20/28 | 4   | DI3/11/19/27 |

| 5   | DI5/13/21/29 | 6   | DI2/10/18/26 |

| 7   | DI6/14/22/30 | 8   | DI1/9/17/25  |

| 9   | DI7/15/23/31 | 10  | DI0/8/16/24  |

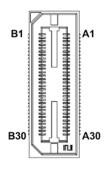

#### **ZIO Expansion Connector (CN5)**

The CN5 is for connecting ZIO module to CPU board.

| Pin | Signal   | Pin | Signal  |

|-----|----------|-----|---------|

|     |          |     | _       |

| A1  | +12V     | B1  | GND     |

| A2  | +5VSB    | B2  | GND     |

| A3  | +5VSB    | B3  | GND     |

| A4  | +3.3VSB  | B4  | GND     |

| A5  | +3.3VSB  | B5  | RSVD    |

| A6  | RSVD     | B6  | RSVD    |

| A7  | RSVD     | B7  | RSVD    |

| A8  | SMB_CLK  | B8  | RSVD    |

| A9  | SMB_DATA | B9  | GND     |

| A10 | GND      | B10 | RSVD    |

| A11 | RSVD     | B11 | RSVD    |

| A12 | RSVD     | B12 | WAKE_N  |

| A13 | RSVD     | B13 | RSVD    |

| A14 | RSVD     | B14 | RSVD    |

| A15 | RSVD     | B15 | GND     |

| A16 | No Use   | B16 | CLK_33M |

| A17 | No Use   | B17 | SERIRQ  |

| A18 | GND      | B18 | LAD0    |

| A19 | No Use   | B19 | LAD1    |

| A20 | No Use   | B20 | LAD2    |

| A21 | PLTRST_N | B21 | LAD3    |

| A22 | No Use   | B22 | L_FRAME |

| A23 | No Use   | B23 | GND     |

| A24 | GND      | B24 | No Use  |

| A25 | No Use   | B25 | No Use  |

| A26 | No Use   | B26 | No Use  |

| A27 | No Use   | B27 | No Use  |

| A28 | No Use   | B28 | GND     |

| A29 | GND      | B29 | No Use  |

| A30 | No Use   | B30 | No Use  |

©Copyright 2015 Axiomtek Co., Ltd. Version A1 April 2015

Printed in Taiwan

94193285000E

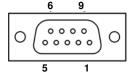

#### **COM Connectors (CN6 and CN7)**

Both CN6 and CN7 are standard DB-9 connectors for COM1 and COM2 interfaces, respectively. Only CN6 comes with power capability on DCD and RI pins by setting JP1.

| Pin | Signal | Pin | Signal |

|-----|--------|-----|--------|

| 1   | DCD    | 6   | DSR    |

| 2   | RXD    | 7   | RTS    |

| 3   | TXD    | 8   | CTS    |

| 4   | DTR    | 9   | RI     |

| 5   | GND    |     |        |

## **Jumper Settings**

Before applying power to AX93285, please make sure all jumper(s) are in factory default positions.

| Jumper                   | Description    | Setting   |

|--------------------------|----------------|-----------|

| JP1 Default, DC 000 Data | CN6 Pin 1: DCD | 3-5 Close |

|                          | CN6 Pin 9: RI  | 4-6 Close |

#### COM1 Data/Power Selection (JP1)

The COM1 port (CN6) has +5V level power capability on DCD and +12V level on RI by setting this jumper.

| Description                          | Setting   |

|--------------------------------------|-----------|

| Power: Set CN6 pin 1 to +5V level    | 1-3 close |

| Data: Set CN6 pin 1 to DCD (Default) | 3-5 close |

| Power: Set CN6 pin 9 to +12V level   | 2-4 close |

| Data: Set CN6 pin 9 to RI (Default)  | 4-6 close |

# **Digital I/O Software Programming**

#### Command byte

The command byte is the first byte to follow the address byte during a write transmission.

| Command | Register      | Command | Register                  |

|---------|---------------|---------|---------------------------|

| 0       | Input port 0  | 4       | Polarity Inversion port 0 |

| 1       | Input port 1  | 5       | Polarity Inversion port 1 |

| 2       | Output port 0 | 6       | Configuration port 0      |

| 3       | Output port 1 | 7       | Configuration port 1      |

94193285000E ©Copyright 2015 Axiomtek Co., Ltd. Version A1 April 2015 Printed in Taiwan 3